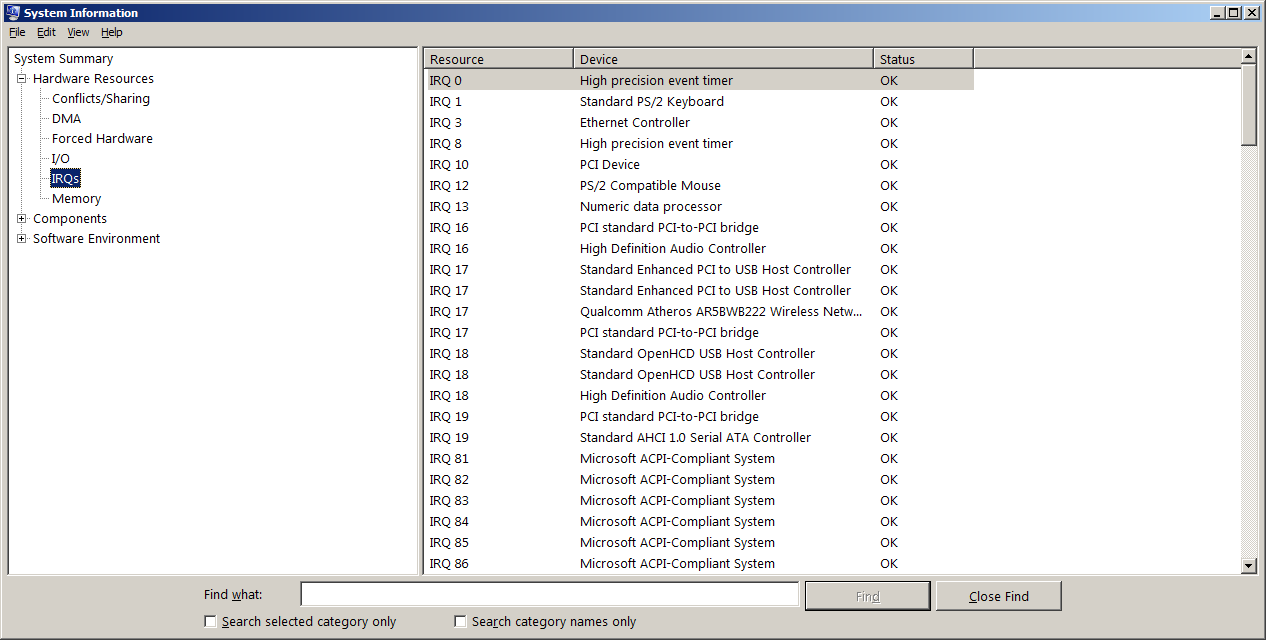

this is on a windows 7 system. obvious we using apic here and not 8259 PIC. can confirm this by checking port 0xa1.

questions here are:

-how are these retrieved.

-are they valid?

IRQ0 would obviously conflict with trap exception for intel's int 0, unless possible to remap the vector offset with an apic as it is possible with PIC?

thanks. sorry - my english is rough still.

questions here are:

-how are these retrieved.

-are they valid?

IRQ0 would obviously conflict with trap exception for intel's int 0, unless possible to remap the vector offset with an apic as it is possible with PIC?

thanks. sorry - my english is rough still.

Attachments